I²C

I²C, für englisch Inter-Integrated Circuit, im Deutschen gesprochen als I-Quadrat-C oder englisch I-Squared-C (ˈaɪ skwɛərd ˈsiː) oder I-2-C (ˈaɪ tuː ˈsiː), ist ein 1982 von Philips Semiconductors (heute NXP Semiconductors) entwickelter serieller Datenbus.

Er wird hauptsächlich geräteintern für die Kommunikation zwischen verschiedenen Schaltungsteilen benutzt, z.B. zwischen einem Controller und Peripherie-ICs. Das ursprüngliche System wurde von Philips in den frühen 1980er Jahren entwickelt, um verschiedene Chips in Fernsehgeräten einfach steuern zu können. Seit Mitte der 1990er Jahre wird I²C auch von einigen Wettbewerbern zur Bezeichnung von Philips-kompatiblen I²C-Systemen verwendet, darunter Siemens AG (später Infineon Technologies AG), NEC, STMicroelectronics, Motorola (später Freescale), Intersil etc. Im Jahr 1998 wurde I²C von über 1000 verschiedenen ICs genutzt und an 50 Firmen lizenziert.

Atmel führte aus lizenzrechtlichen Gründen die heute auch von einigen anderen Herstellern verwendete Bezeichnung TWI (Two-Wire-Interface, englisch für Zweidraht-Schnittstelle)[Anm. 1] ein; technisch sind TWI und I²C praktisch[Anm. 2] identisch. Allerdings ist das ursprüngliche Patent am 1. Oktober 2006 ausgelaufen, so dass keine Lizenzgebühren für die Benutzung von I²C mehr anfallen. I²C ist auch kein eingetragenes Markenzeichen von NXP Semiconductors, Markenschutz besteht lediglich für das Logo.

Geschichte

Der Bus wurde 1982 von Philips eingeführt zur geräteinternen Kommunikation zwischen ICs in z.B. CD-Spielern und Fernsehgeräten. Dazu wurde die Mikrocontroller-Familie MAB8400 entwickelt, die einen I²C-Bus-Controller enthielt. Die erste standardisierte Spezifikation 1.0 wurde 1992 veröffentlicht. Diese ergänzte den ursprünglichen Standard mit 100 kbit/s um einen neuen „schnellen“ Modus (Fast-mode) mit 400 kbit/s und erweiterte den Adressraum um einen 10-Bit-Modus, so dass statt der ursprünglichen 112 Knoten seitdem bis zu 1136 unterstützt werden.

Mit Version 2.0 aus dem Jahr 1998 kam ein „Hochgeschwindigkeitsmodus“ (Hs-mode) mit max. 3,4 Mbit/s dazu, wobei die Strom- und Spannungsanforderungen in diesem Modus gesenkt wurden. Version 3.0 von 2007 führte einen weiteren Modus „Fast-mode Plus“ (Fm+) mit bis zu 1 Mbit/s ein, der im Gegensatz zum Hs-mode dasselbe Protokoll verwendet wie die 100- und 400-kbit/s-Modi.

Im Jahr 2012 wurde mit der Spezifikation V.4 ein noch schnellerer Modus „Ultra Fast-mode“ (Ufm) eingeführt, der unidirektionale Übertragungsraten bis zu 5 Mbit/s unterstützt. Im selben Jahr wurden mit der aktuellen V.5 einige Fehler der Vorgängerversion korrigiert. Im April 2014 erschien V.6, die erneut Fehler korrigierte.

Bussystem

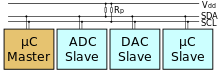

I²C ist als Master-Slave-Bus konzipiert. Ein Datentransfer wird immer durch einen Master initiiert; der über eine Adresse angesprochene Slave reagiert darauf. Mehrere Master sind möglich (Multimaster-Betrieb). Wenn im Multimaster-Betrieb ein Master-Baustein auch als Slave arbeitet, kann ein anderer Master direkt mit ihm kommunizieren, indem er ihn als Slave anspricht.

Elektrische Definition

Im Diagramm rechts sind drei Geräte eingezeichnet. I²C benötigt zwei Signalleitungen: Takt- (SCL = Serial Clock) und Datenleitung (SDA = Serial Data). Beide liegen mit den Pull-up-Widerständen RP an der Versorgungsspannung VDD. Sämtliche daran angeschlossene Geräte haben Open-Collector-Ausgänge, was zusammen mit den Pull-up-Widerständen eine Wired-AND-Schaltung ergibt. Der High-Pegel soll mindestens 0,7 × VDD betragen, und der Low-Pegel soll bei höchstens 0,3 × VDD liegen. Die im Bild nicht eingezeichneten Serienwiderstände RS an den Eingängen der Geräte sind optional und werden als Schutzwiderstände verwendet. Der I²C-Bus arbeitet mit positiver Logik, d.h. ein High-Pegel auf der Datenleitung entspricht einer logischen „1“, der Low-Pegel einer „0“.

Takt und Zustände des Busses

Der Bustakt wird immer vom Master ausgegeben. Das Taktsignal liegt nicht ständig an, sondern nur während der Datenübertragung. Für die verschiedenen Modi ist jeweils ein maximal erlaubter Bustakt vorgegeben. In der Regel können aber auch beliebig langsamere Taktraten verwendet werden, falls diese vom Master-Interface unterstützt werden. Einige ICs (z.B. Analog-Digital-Umsetzer) benötigen jedoch eine bestimmte minimale Taktfrequenz, um ordnungsgemäß zu funktionieren.

| Modus | Maximale Übertragungsrate |

Richtung |

|---|---|---|

| Standard Mode (Sm) | 0,1 Mbit/s | bidirektional |

| Fast Mode (Fm) | 0,4 Mbit/s | |

| Fast Mode Plus (Fm+) | 1,0 Mbit/s | |

| High Speed Mode (Hs-mode) | 3,4 Mbit/s | |

| Ultra Fast-mode (UFm) | 5,0 Mbit/s | unidirektional |

Wenn der Slave mehr Zeit benötigt, als durch den Takt des Masters vorgegeben ist, kann er zwischen der Übertragung einzelner Bytes die Taktleitung auf „low“ halten (Clock-Stretching) und so den Master bremsen. In der Spezifikation einiger Slave-Bausteine wird explizit erklärt, dass sie kein Clock Stretching anwenden. Dementsprechend gibt es auch Bustreiber-Bausteine, die so ausgelegt sind, dass sie das Taktsignal nur in eine Richtung übertragen können.

Daten (Einzelbits) sind nur gültig, wenn sich ihr logischer Pegel während einer Clock-High-Phase nicht ändert. Ausnahmen sind das Start-, Stop- und Repeated-Start-Signal. Das Start-Signal ist eine fallende Flanke auf SDA, während SCL high ist, das Stop-Signal ist eine steigende Flanke auf SDA, während SCL high ist. Repeated-Start sieht genauso aus wie das Start-Signal.

Eine Dateneinheit besteht aus 8 Datenbits = 1 Oktett (welche protokollbedingt entweder als Wert oder als Adresse interpretiert werden) und einem ACK-Bit. Dieses Bestätigungsbit (Acknowledge) wird vom Slave durch einen Low-Pegel auf der Datenleitung während der neunten Takt-High-Phase (welche nach wie vor vom Master generiert wird) und als NACK (für engl. not acknowledge) durch einen High-Pegel signalisiert. Der Slave muss den Low-Pegel an der Datenleitung anlegen, bevor SCL auf high geht, andernfalls lesen weitere eventuelle Teilnehmer ein Start-Signal.

Adressierung

Eine Standard-I²C-Adresse ist das erste vom Master gesendete Byte, wobei die ersten sieben Bit die eigentliche Adresse darstellen und das achte Bit (R/W-Bit) dem Slave mitteilt, ob er Daten vom Master empfangen soll (Low: Schreibzugriff) oder Daten an den Master zu übertragen hat (High: Lesezugriff). I²C nutzt daher einen Adressraum von 7 Bit, was bis zu 112 Knoten auf einem Bus erlaubt (16 der 128 möglichen Adressen sind für Sonderzwecke reserviert).

Jedes I²C-fähige IC hat eine (üblicherweise vom Hersteller) festgelegte Adresse, von der in der Regel eine modellabhängige Anzahl der untersten Bits (LSB) über spezielle Eingangspins des ICs individuell konfiguriert werden können. Hierdurch wird es möglich, mehrere ICs dieses Typs am selben I²C-Bus zu betreiben, ohne dass es zu Adresskonflikten kommt. Lassen sich Adresskonflikte nicht vermeiden, so müssen die entsprechenden ICs mit getrennten I²C-Bussen angesteuert oder temporär vom Bus getrennt werden.

Wegen Adressknappheit wurde später eine 10-Bit-Adressierung eingeführt. Sie ist abwärtskompatibel zum 7-Bit-Standard durch Nutzung von 4 der 16 reservierten Adressen. Beide Adressierungsarten sind gleichzeitig verwendbar, was bis zu 1136 Knoten auf einem Bus erlaubt.

Übertragungsprotokoll

Der Beginn einer Übertragung wird mit dem Start-Signal vom Master angezeigt, dann folgt die Adresse. Diese wird durch das ACK-Bit vom entsprechenden Slave bestätigt. Abhängig vom R/W-Bit werden nun Daten byteweise geschrieben (Daten an Slave) oder gelesen (Daten vom Slave). Das ACK beim Schreiben wird vom Slave gesendet und beim Lesen vom Master. Das letzte Byte eines Lesezugriffs wird vom Master mit einem NACK quittiert, um das Ende der Übertragung anzuzeigen. Eine Übertragung wird durch das Stop-Signal beendet. Alternativ kann auch ein Repeated-Start am Beginn einer erneuten Übertragung gesendet werden, ohne die vorhergehende Übertragung mit einem Stop-Signal zu beenden.

Alle Bytes werden dabei „Most Significant Bit First“ übertragen.

Für den High-Speed-Mode wird zuerst im Fast oder Standard Mode ein Master-Code geschickt, bevor auf die erhöhte Frequenz umgeschaltet wird. Dadurch wird zum einen der High-Speed-Mode signalisiert, zum anderen haben nicht High-Speed-taugliche Busteilnehmer die Chance, innerhalb ihrer Spezifikation zu erkennen, dass sie nicht angesprochen wurden. Im Multimasterbetrieb muss jeder Busmaster einen eigenen Master-Code benutzen. So ist sichergestellt, dass die Busarbitrierung (s.u.) abgeschlossen ist, bevor in den High-Speed-Mode gewechselt wird.

Arbitrierung im Multimaster-Betrieb

Die Arbitrierung (Zugriffsregelung auf den Bus) ist durch die Spezifikation geregelt: Der Bus ist zwischen Start- und Stoppsignal belegt. Busmaster müssen daher immer auf Start- und Stoppsignale achten, um den Überblick über den Busstatus zu behalten. So können sie warten, bis der Bus frei ist, sollte (evtl. unvorhergesehen) eine Übertragung anstehen.

Sollten mehrere Busmaster gleichzeitig mit einer Transaktion starten wollen, so sehen sie den Bus als frei an und starten gleichzeitig mit der Übertragung. Sind die Master unterschiedlich schnell, erfolgt die Übertragung nun zunächst so schnell, wie der langsamste der beteiligten Busmaster arbeitet, da das Taktsignal eines langsameren Busmasters per Clock-Stretching die schnelleren ausbremst. Alle Busmaster lauschen auf die von ihnen selbst gesendeten Daten. In dem Augenblick, wenn ein Busmaster eine „0“ und ein anderer eine „1“ übertragen will, nimmt die Bus-Leitung (aufgrund der Wired-And-Schaltung aller Busteilnehmer) „0“-Pegel an. Gemäß dem I²C-Protokoll verlieren in diesem Augenblick die Busmaster mit der „1“ den Bus, ziehen sich zurück und warten auf das Stoppsignal, um dann ihr Glück erneut zu versuchen. Die anderen Busmaster machen weiter, bis schließlich nur noch einer übrigbleibt. Sollte ein unterlegener Busmaster-Baustein auch Slave-Dienste anbieten, muss er allerdings gleichzeitig darauf achten, ob der gewinnende Busmaster ihn gerade ansprechen will und daher gerade dabei ist, ihn zu adressieren.

Das Verfahren geht so weit, dass gar keine Arbitrierung stattfindet, wenn mehrere Busmaster zufällig – über mehrere Bytes hinweg von Anfang bis zum Abschluss ihrer jeweiligen Transaktionen hinweg – identische Daten an denselben Slave-Baustein senden: Die betreffenden Busmaster merken nichts voneinander – eventuelles Clock-Stretching durch einen langsameren Master ist gemäß Protokoll nicht von Clock-Stretching durch den Slave zu unterscheiden; der angesprochene Slave-Baustein kommuniziert mit den betreffenden Busmastern gleichzeitig, ohne dass es von den Beteiligten bemerkt wird. Diese Tatsache ist zu berücksichtigen, und ihr muss, sofern sie sich störend auswirken könnte, anderweitig Abhilfe geschaffen werden.

Verwendung

Eine Eigenschaft von I²C ist die Tatsache, dass ein Mikrocontroller ein ganzes Netzwerk an integrierten Schaltungen mit nur zwei I/O-Pins und einfacher Software kontrollieren kann. Busse dieses Typs wurden realisiert, da ein nicht unerheblicher Teil der Kosten einer integrierten Schaltung und der verwendeten Leiterplatte von der Größe des Gehäuses und der Anzahl der Pins abhängt. Ein großes IC-Gehäuse hat mehr Pins, braucht mehr Platz auf der Leiterplatte und hat mehr Verbindungen, die versagen können. All das steigert die Produktions- und Testkosten.

Obwohl langsamer als neuere Bus-Systeme, ist I²C wegen des geringen Aufwands vorteilhaft für Peripheriegeräte, die nicht schnell zu sein brauchen. Häufig wird er für die Übertragung von Steuer- und Konfigurationsdaten verwendet. Beispiele sind Lautstärkeregler, Analog-Digital- oder Digital-Analog-Wandler mit niedriger Abtastrate, Echtzeituhren, kleine, nichtflüchtige Speicher oder bidirektionale Schalter und Multiplexer. Auch elektronische Sensoren haben oft einen Analog-Digital-Wandler mit I²C-Schnittstelle integriert.

Während des Betriebes können Chips zum Bus hinzugefügt oder entfernt werden (Hot-Plugging).

I²C wird auch als Basis für ACCESS.bus und VESAs Monitordaten-Interface (Display Data Channel, kurz DDC) benutzt. Der vom Prozessorhersteller Intel für die Kommunikation von Mainboard-Komponenten definierte SMBus ist dem I²C-Bus sehr ähnlich, die meisten ICs erlauben einen Betrieb an beiden Bussen.

Große Bedeutung hatte das I²C-Protokoll in der Vergangenheit im Chipkartenbereich. Die in Deutschland bis Ende 2014 verwendete Krankenversichertenkarte war eine I²C-Karte, d.h. unter den goldenen Kontaktflächen der Chipkarte befand sich ein einfaches I²C-EEPROM, das vom Kartenleser über das I²C-Protokoll ausgelesen und beschrieben werden konnte.

Stabilität

Das Protokoll des I²C-Bus ist von der Definition her recht einfach, aber auch recht störanfällig. Diese Tatsache schränkt die Verwendung auf störarme Umgebungen ein, wo weder mit Übersprechen, Rauschen, EMV-Problemen noch mit Kontaktproblemen (Stecker, Buchsen) zu rechnen ist. Auch ist er ungeeignet zur Überbrückung größerer Entfernungen, wie es beispielsweise für Feldbusse typisch ist.

Der Bus kann jedoch mit speziellen Treibern auf einen höheren Strom- oder Spannungspegel umgesetzt werden, wodurch der Störabstand und die mögliche Leitungslänge steigen. Ein noch größerer Störabstand ist durch eine Umsetzung auf den physikalischen Layer des CAN-Busses möglich, der mit differentiellen Open-Collector-Signalen arbeitet. Störungen sowohl des SDA- als auch des SCL-Signals resultieren in fehlerhaft übertragenen Daten, die vor allem bei Störungen auf SDA oft nicht erkannt werden können. Lediglich bei geringen, zeitlich begrenzten Störungen, z.B. weit oberhalb der Signalfrequenz, kann das System mittels Signalverarbeitung stabiler gemacht werden.

Die eigentliche I²C-Spezifikation beinhaltet (anders als die SMBus-Spezifikation) keinen Timeout; dadurch kann es unter bestimmten Umständen dazu kommen, dass Busteilnehmer den Bus blockieren. Falls ein Slave-Chip gerade die Datenleitung auf „0“ zieht, während der Master den Transfer (beispielsweise durch einen Reset) abbricht, bleibt die Datenleitung für unbestimmte Zeit auf „0“. Somit bleibt der gesamte I²C-Bus mit allen angeschlossenen Teilnehmern (Chips) blockiert. Daher sollen im Falle eines Resets auch alle Busteilnehmer zurückgesetzt werden, ggf. durch Unterbrechen der Spannungsversorgung. Alternativ wird ein Bus clear durchgeführt: Der Master generiert bis zu neun Taktimpulse; spätestens dann sollte die Datenleitung freigegeben sein. Selbst wenn sich der Slave-Baustein noch mitten in einer Übertragung befindet und die Datenleitung nur freigegeben ist, weil er gerade eine „1“ ausgibt, wird er (bzw. dessen I²C-Komponente) durch das nächste Start-Signal zurückgesetzt. Analog Devices empfiehlt, zunächst ein Stopp-Signal zu senden.

Erweiterungen

Die MIPI Alliance hat 2014 ein I3C genanntes, zu I²C abwärtskompatibles Interface vorgestellt. Es wird als Nachfolger von I²C propagiert. Es enthält Erweiterungen wie eine höhere Übertragungsgeschwindigkeit (High Data Rate – HDR) und kann damit bei mittleren Geschwindigkeiten auch das Serial Peripheral Interface (SPI) ersetzen.

Anmerkungen

- ↑ Gezählt werden hier nur die Signalleitungen, nicht aber die Leitung für das Bezugspotential (Masseleitung)

- ↑ Kleine Unterschiede in der Implementierung listet beispielhaft das Datenblatt für AT32UC3A… auf Seite 220 auf.

© biancahoegel.de

Datum der letzten Änderung: Jena, den: 14.06. 2024