Integrierter Schaltkreis

Ein integrierter Schaltkreis, auch integrierte Schaltung (englisch integrated circuit, kurz IC; die Buchstaben werden einzeln gesprochen: [ʔiː] [t͡seː] bzw. veraltet IS) ist eine auf einem dünnen, meist einige Millimeter großen Plättchen aus Halbleiter-Material aufgebrachte elektronische Schaltung. Sie wird manchmal auch als Festkörperschaltkreis oder monolithischer Schaltkreis (englisch solid-state circuit bzw. monolithic integrated circuit) bezeichnet. Dieser Chip (englisch Die) ist meist zum Schutz und zur einfacheren Kontaktierung in einem mehrfach größeren Chipgehäuse eingekapselt. Ein IC enthält typischerweise eine Kombination von zahlreichen miteinander elektrisch verbundenen elektronischen Halbleiterbauelementen wie Transistoren, Dioden und/oder weiteren aktiven und passiven Bauelementen.

Integrierte Schaltkreise können heutzutage Schaltungen mit vielen Milliarden elektronischen Bauelementen (insbesondere Transistoren) umfassen, so dass auch hochkomplexe Schaltungen wie Mikroprozessoren und Speicherchips auf wenige Quadratmillimeter kleinen Halbleiterplättchen untergebracht werden können. Seit Anfang der 1990er Jahre werden die Mikrostrukturen dieser Elemente schon im Nanometer-Bereich gefertigt. Die rechteckigen Halbleiterplättchen werden Chip genannt (auch schon im Rohzustand), insbesondere zusammen mit dem aufgebrachten elektronischen Schaltkreis auch Mikrochip. Die Herstellung von ICs erfolgt in eigenen Halbleiter-Fabriken in absolut staubfreien Reinräumen und umfasst eine Vielzahl von Prozessschritten physikalischer und chemischer Art. Da generell die Leistungsfähigkeit von Mikroprozessoren und Speicherchips mit kleiner werdenden Strukturen auf dem Chip zunimmt, bewegt sich deren Miniaturisierung oft an der Grenze des technisch und physikalisch Machbaren. Es existieren jedoch auch zahlreiche, insbesondere standardisierte ICs wie Logikbausteine und Operationsverstärker, wo dies nur eine geringe Rolle spielt – so enthalten die Logik-Chips der weit verbreiteten, bereits seit den 1970ern hergestellten 74xx-Serie nur eine Anzahl Transistoren im ein- oder zweistelligen Bereich.

Sprachgebrauch

Umgangssprachlich wird inzwischen Mikrochip bzw. Chip teilweise mit einem IC gleichgesetzt, obwohl der Chip nur das „Innenleben“ eines Schaltkreises darstellt, also das englisch als Die bezeichnete Halbleiterplättchen mit der eigentlichen Schaltung darauf.

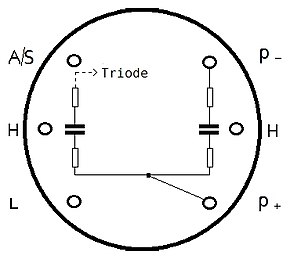

Abzugrenzen von integrierten Schaltkreisen sind außerdem Doppel-, Dreifach- oder weitere Mehrfach-Bauelemente (unabhängig ob als Halbleiter-Bauelement oder Röhre), die sich jeweils in einem gemeinsamen Gehäuse oder Glaskolben wie Doppel-Dioden, -Trioden, -Pentoden, Doppel- bzw. Dreifach-Darlington-Transistoren usw. befinden.

Geschichte

• Triode: zur inneren Triode

• A(ntenna)/S(tation select): Antenne/Senderwahl

• P(ower)+/-: Batterie

• H(eating): Röhrenheizung

• L(oudspeaker): Lautsprecher/Kopfhörer

Vorgänger

Vor der Entwicklung integrierter Schaltungen gab es aktive elektronische Bauelemente, die zusammen mit mehreren passiven fest verdrahtet und in einem Gehäuse ausgeliefert wurden. Ein Beispiel waren die Mitte der 1920er Jahre entwickelten Elektronen- bzw. Vakuumröhren 3NF und 2HF – erstere eine Dreifachröhre, ähnlich der späteren Doppel-Triode ECC83. Im Unterschied zu der jüngeren Röhre waren bei beiden 1920er-Röhren, wie in einem IC, jedoch zusätzlich bereits im Inneren des Kolbens der Röhre vier bzw. zwei Widerstände und zwei oder ein Kondensator eingearbeitet. Daraus resultierten fertige Radio-Schaltungen – die 3NF als Basisschaltung zum Ortsempfang und Verstärkung und die 2HF zusätzlich zum optionalen Fernempfang, bei denen lediglich die Außenkomponenten zur Senderwahl, Spannungsversorgungen und Wiedergabe (Lautsprecher oder Kopfhörer) sowie die Antenne angeschlossen werden mussten.

Bis Ende der 1950er Jahre wurden elektronische Schaltungen mit diskreten Bauteilen aufgebaut, d.h. mit einzelnen Transistoren, Dioden etc., die auf einer Leiterplatte zu einer Schaltung zusammengefügt wurden. Dies war hinsichtlich Größe und Lebensdauer bereits ein wesentlicher Durchbruch gegenüber den damals konkurrierenden Elektronenröhren.

Zwar gab es schon vor der Erfindung des Transistors elektronische Bauelemente, die mehrere Funktionen in einem Bauteil integrierten, in Form von Mehrsystemröhren, Verbundröhren wie der 3NF, Duodioden oder auch mehranodigen Quecksilberdampfgleichrichtern, die in einem Bauteil die Funktion mehrerer gesteuerter oder ungesteuerter Gleichrichter (eine Kathode und mehrere Anoden) vereinten. Transistoren weisen gegenüber den Vakuumröhren entscheidende Vorteile auf, z.B. geringere Leistungsaufnahme und Größe. Mit der Anwendung von Leiterplatten bzw. Platinen und der daraus resultierenden Verkleinerung der Produkte begann diese neuere Technik die frühen röhrenbasierten integrierten Systeme zu verdrängen. Dieser Trend verstärkte sich mit der Entwicklung und dem massiven Einsatz von integrierten Schaltungen ab den 1960er Jahren vollends.

Jacobi-Patent

Kaum bekannt ist der bereits 1949 von Werner Jacobi erfundene und patentierte „Halbleiterverstärker“, eine Schaltung aus fünf Transistoren auf einem als Trägermaterial dienenden Halbleiter. Diese bilden eine dreistufige Verstärkerschaltung in Form eines integrierten Schaltkreises. Zwei Transistoren werden „über Kopf“ geschaltet und bewirken damit die Impedanzwandlung zwischen den Transistorstufen. Jacobi hielt fest, dass damit zum Beispiel Hörgeräte klein, leicht und billig realisiert werden können.

Eine umgehende wirtschaftliche Nutzung seines Patentes ist nicht bekannt. Die Formulierung des Integrationsgedankens in der am 15. Mai 1952 bekannt gemachten Patentschrift lautet: „Halbleiterverstärker, dadurch gekennzeichnet, daß auf den Halbleiter mehrere in verschiedenen Schalt- bzw. Verstärkerstufen wirkende Elektrodensysteme aufgesetzt werden.“ Damit geht zum Beispiel die Integration mehrerer Leuchtdioden in ein Gehäuse im Grundgedanken auf Jacobi zurück.

Von Kilby und Noyce bis heute

Der erste integrierte Schaltkreis (ein Flipflop) wurde im September 1958 von Jack Kilby entwickelt. Er bestand aus zwei Bipolartransistoren, welche auf einem Germanium-Substrat befestigt und durch Golddrähte verbunden wurden. Dieser Hybrid-Schaltkreis ist somit ein erstes Beispiel der Umsetzung der schon bekannten Transistor-Transistor-Logik (TTL) auf einen Schaltkreis. Sie war eine Vorstufe zur Weiterentwicklung der TTL-Schaltungen hin zu kleineren Bauformen.

Den ersten „monolithischen“, d.h. aus bzw. in einem einzigen einkristallinen Substrat gefertigten, integrierten Schaltkreis meldete Robert Noyce im Juli 1959 zum Patent an. Das Entscheidende an der Erfindung von Noyce war die komplette Fertigung der Bauelemente einschließlich Verdrahtung auf einem Substrat. Für die Herstellung wurden bereits fotolithografische Verfahren und Diffusionsprozesse genutzt, die Fairchild Semiconductor kurz zuvor für die Herstellung des ersten modernen Diffusions-Bipolartransistors entwickelt hatte. Unter anderem auf diesen Techniken basierend wurden 1970/71 nahezu gleichzeitig die ersten Mikroprozessoren von drei Firmen vorgestellt: der Intel 4004, der Texas Instruments (TI) TMS 1000 und der Garrett AiResearch „Central Air Data Computer“ (CADC).

Die ersten integrierten Schaltkreise in Serienproduktion entstanden Anfang der 1960er Jahre (vor allem bei Texas Instruments und Fairchild Semiconductor). Sie bestanden lediglich aus bis zu wenigen Dutzend Bipolar-Transistoren (englisch small-scale integration, SSI), typischerweise in RTL-Technik. Mit den Jahren wurden die Bauelemente jedoch immer weiter verkleinert, passive Bauelemente wie Widerstände integriert sowie die Komplexität der integrierten Schaltkreise gesteigert. Damit erhöhte sich auch die Anzahl der Transistoren pro Chip beziehungsweise pro Flächeneinheit; dabei war die Anzahl der Transistoren die wichtigste Kenngröße von ICs.

Ein fördernder Faktor für die Weiterentwicklung waren die Rüstungsindustrie und die Raumfahrt. Bis Mitte der 1960er Jahre war die US-Regierung Hauptabnehmer integrierter Schaltkreise. Ziel war die Miniaturisierung der Technik beider Bereiche. Ab 1965 erfolgte die Ausrüstung des Gemini-Programms mit Bord-Computern auf Basis von ICs.

Mit der medium-scale integration (MSI) fanden einige hundert Transistoren, bei der large-scale integration (LSI) Anfang der 1970er einige tausend Transistoren Platz auf einem Chip. Damit war es erstmals möglich, einen ganzen Hauptprozessor (CPU) als sogenannten Mikroprozessor auf einem Chip zu integrieren, was die Kosten für Computer extrem reduzierte. Anfang der 1980er folgte die very-large-scale integration (VLSI) mit einigen hunderttausend Transistoren, mittels derer man schon bald Speicherchips (RAM) mit einer Kapazität von 256 KiBit und 1 MiBit herstellen konnte. Mit dieser Weiterentwicklung der Fertigungstechnologie ging eine immer höhere Entwurfsautomatisierung des Designs und der zur Fertigung erforderlichen Fotomasken einher, ohne die eine Entwicklung komplexerer Schaltungen nicht mehr möglich war.

Im Jahr 2010 enthielten Grafik-Prozessoren bis zu drei Milliarden Transistoren, „normale“ General-Purpose-CPUs bis zu 1,17 Milliarden Transistoren (Intel Core i7-980X). Der Itanium 2 Tukwila besteht aus 2,05 Milliarden Transistoren. Mittlerweile sind Grafikprozessoren bei Transistorzahlen von über acht Milliarden Transistoren angelangt. Noch größere Zahlen werden bei Speicherbausteinen erreicht, bei allerdings geringerer Komplexität des gesamten Chips.

-

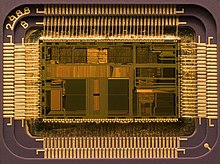

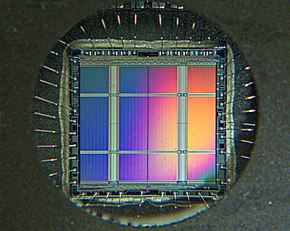

Verschiedene ICs

Verschiedene ICs -

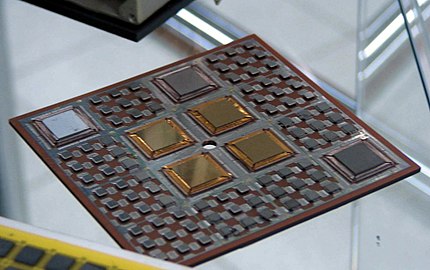

ICs auf TCM-Keramikträger aus einem IBM Mainframe

ICs auf TCM-Keramikträger aus einem IBM Mainframe -

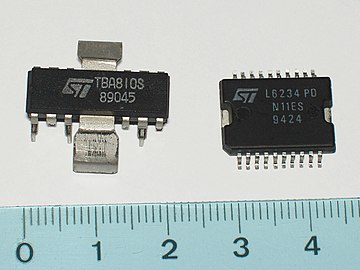

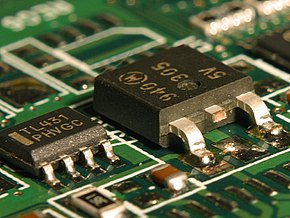

ICs im Kunststoffgehäuse. Die großflächigen Metallfahnen (beim rechten Baustein in den Kerben) dienen der Wärmeabfuhr, sie können auf eine große Massefläche gelötet oder mit einem Kühlkörper versehen werden.

ICs im Kunststoffgehäuse. Die großflächigen Metallfahnen (beim rechten Baustein in den Kerben) dienen der Wärmeabfuhr, sie können auf eine große Massefläche gelötet oder mit einem Kühlkörper versehen werden. -

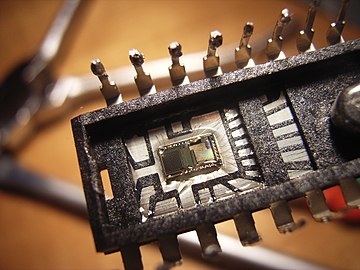

ICs im Chipgehäuse mit Anschlussdrähten

ICs im Chipgehäuse mit Anschlussdrähten

Arten und Anwendung

Überblick

Das Hauptmerkmal von integrierten Schaltungen ist eine große Zahl an verschiedenartigen oder gleichen aktiven und passiven Bauelementen – zu letzteren gehören Widerstände und Kondensatoren – sowie verbindenden Leiterzügen auf oder in einem einkristallinen Substrat. Damit bilden sie das Pendant zu Schaltkreisen aus auf einer Leiterplatte gelöteten einzelnen (diskreten) Bauelementen. Eine Zwischenstellung nehmen Dickschicht- und Dünnschichtschaltungen – wobei Bauteile durch Aufdampfen und Strukturieren einer dünnen Schicht auf einem Glassubstrat hergestellt werden – sowie (Hybridschaltkreise) ein. Es gibt eine Reihe weiterer Unterscheidungen:

Nach der Fertigungstechnologie

- monolithische Schaltkreise: es werden alle Bauelemente auf einem einzigen Stück (Substrat) einkristallinen Halbleitermaterials (Chip) hergestellt; die Schaltkreise werden dabei meist durch Dotierung oder Epitaxie an der Oberfläche des Substratmaterials (Dioden, Transistoren, bis zu einigen Mikrometern ober- und unterhalb der ursprünglichen Oberfläche) oder durch Schichtauftrag (Widerstände, Leiterzüge, Kondensatoren, Isolationen, Gates von MOSFET, Epitaxie) gefertigt.

- Dünnschicht-Schaltkreise sind Bauelemente, die durch Bedampfen auf einem Glassubstrat hergestellt werden. Es handelt sich meist um Widerstands-Netzwerke. Sie können durch Elektronenstrahlabgleich auch in höchster Genauigkeit gefertigt werden. Sie sind durch Tauchlackierung geschützt. Ebenfalls in diese Gruppe gehören Schaltungen aus Dünnschichttransistoren (TFT), wie sie z.B. in Flachbildschirmen Anwendung finden.

- Dickschicht-Hybridschaltkreise vereinen mehrere monolithische Chips sowie gedruckte Leiterzüge und passive Bauteile (fast nur Widerstände) in Dickschicht-Technologie meist auf einem Keramikträger; sie sind oft tauchlackiert.

Nach der Signalart

- Digitale ICs verarbeiten oder speichern Signale, die in Form von wenigen diskreten Pegeln vorliegen.

- Analoge (Linear-) ICs verarbeiten Signale mit beliebigen Zwischenwerten.

- Mixed-Signal-ICs haben sowohl analoge als auch digitale Schaltungsteile.

Sensor- und Aktor-ICs sind Wandler zwischen unterschiedlichen physikalischen Größen, die mit mikroelektronischen Technologien gefertigt werden. Beispiele sind ICs in CMOS-Kameras, Mikrospiegelaktoren, Hallsonden, Beschleunigungssensoren oder Schaltkreise zur Messung ihrer Temperatur, der Beleuchtungsstärke oder zum Empfang digitaler Infrarot-Signale

Nach der Aufgabe

- Prozessoren dienen als Rechen- und Steuereinheiten von Computern

- Halbleiterspeicher speichern digitale Daten

- Miniaturisierte Chips im Rahmen der RFID-Technologie zur kontaktlosen Identifikation von Gegenständen und Lebewesen

- Standard-Logik-ICs verschiedener Logikfamilien bieten anwendungsübergreifende Funktionen

- ASICs sind anwendungsspezifische Entwicklungen (z.B. in Toastern, im Kfz, in Waschmaschinen)

- ASSPs sind anwendungsspezifische Standardprodukte, die ähnlich wie ASICs Spezialanwendungen haben, aber vom Hersteller angeboten werden und nicht auf Wunsch des Kunden gebaut werden

- Sensor-ICs wandeln und verarbeiten nichtelektrische Größen (z.B. Beschleunigung, Licht, Magnetfelder)

- DSPs (digitale Signalprozessoren) verarbeiten digitale Signale oder analoge Signale in digitaler Form

- D/A- und A/D-Wandler wandeln digitale in analoge Werte oder umgekehrt

- FPGAs (engl. field programmable gate array) sind vom Kunden konfigurierbare digitale ICs, die aus einer Vielzahl von zusammenschaltbaren Funktionseinheiten bestehen

- Mikrocontroller (µC) enthalten alle Teile eines kleinen Computers (Programmspeicher, Rechenwerk, Arbeitsspeicher und Register)

- Leistungs-ICs können hohe Ströme und Spannungen verarbeiten (z.B. als komplette Leistungs-Verstärker oder in Netzteilen)

- System-on-a-Chip (SoC) sind größere Systeme, die auf einem Chip vereint werden

Herstellung

Überblick

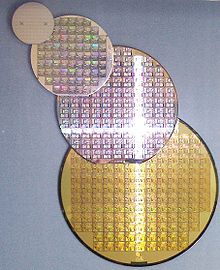

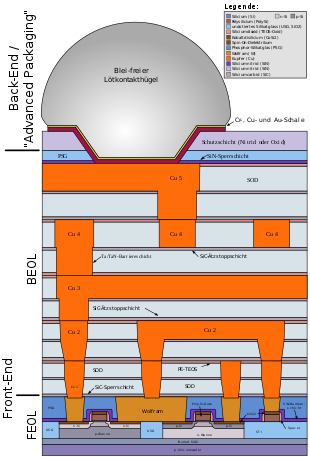

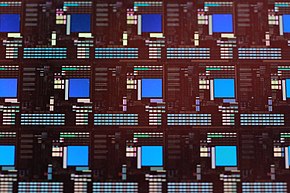

Die Fertigung von integrierten Schaltungen erfolgt vollständig auf Wafern (einkristalline Halbleiterscheibe), man spricht daher auch von einer „monolithischen Fertigung“ oder „monolithischen Integration“. Dabei werden auf einem 300-mm-Wafer zwischen ca. 80 (bei sehr großen Prozessoren meist mit größerem Cache, z.B. Intel Tukwila) und mehr als Zehntausend (bei Einzeltransistoren, einfachen Schaltungen, LEDs, Photodioden etc.) meist identische integrierte Schaltkreise parallel hergestellt, was unter anderem die Herstellungskosten senkt. Der Fertigungsprozess kann (neben Funktionstests) in drei grundlegende Abschnitte eingeteilt werden:

- Die Substratherstellung, dazu gehört die Aufreinigung des Ausgangsmaterials, Herstellung von großen Einkristallen (sog. Ingots) und Einzelsubstraten (Wafern)

- Die Herstellung der einzelnen Bauelemente auf einem Wafer, das sogenannte

Front-End. Dieser Schritt lässt sich nochmals unterteilen in:

- Front-End-of-Line (engl. front-end of line, FEOL, dt. ‚vorderes Ende der Produktionslinie‘): Hier werden die (aktiven) Bauelemente wie Transistoren, Dioden oder Kondensatoren durch die Bearbeitung des Substratmaterials hergestellt.

- Back-End-of-Line (engl. back-end of line, BEOL, dt. ‚hinteres Ende der Produktionslinie‘): Dieser Schritt umfasst im Wesentlichen die sogenannte Metallisierung, bei der die im FEOL gefertigten Bauelemente miteinander verbunden werden, und die abschließende Passivierung der Oberfläche.

- Das Zerteilen der Wafer in Einzelchips und deren Verpacken in Gehäuse, das sogenannte Back-End (nicht zu verwechseln mit Back-End-of-Line).

Eine „hybride Integration“ (Hybridtechnik) – eine Kombination von Bauelementen aus unterschiedlichen Werkstoffen und Fertigungsprozessen, wie der Dünn- und Dickfilmtechnik – wie sie unter anderem bei der Herstellung von Mikrosystemen genutzt wird, findet bei der Herstellung von integrierten Schaltkreisen bislang keine Anwendung. Ein vergleichbarer Aufbau, der 3D-Integration, bei dem mehrere Chips übereinandergestapelt und elektrisch miteinander verbunden werden, könnte aber in zukünftigen ICs Verwendung finden.

Substratherstellung

Das Grundmaterial (Substrat) dient in der Regel sowohl als Träger als auch als Basismaterial für die aktiven Gebiete von Dioden und Transistoren. Mehr als 99 Prozent der integrierten Schaltkreise nutzen Silicium als Substratmaterial. Für sehr hochfrequente oder optische Anwendungen kommen auch andere Materialien wie Galliumarsenid zum Einsatz. Für spezielle Anwendungen werden Silicon-on-Insulator-Substrate (SOI-Substrate) oder Silicium auf dem isolierenden Substrat wie Saphir verwendet (engl. Silicon-on-Sapphire, SOS).

Damit die hohen Anforderungen der Mikroelektronik erfüllt werden können, muss das Substrat in Form von hochreinen Einkristallen hergestellt werden. Im Falle des Siliciums wird zunächst aus einer hochreinen Siliciumschmelze (vgl. Gewinnung von Reinsilicium) ein einkristalliner Zylinder (Ingot) gezogen. Dazu wird vornehmlich das sogenannte Czochralski-Verfahren (CZ-Verfahren) genutzt. Ein alternatives Verfahren ist das Zonenschmelzen, was auch zur weiteren Reinigung der CZ-Ingots eingesetzt werden kann; für einige Spezialanwendungen sind höhere Reinheitsgrade notwendig als ein Fremdatom auf 109 Atomen der CZ-Ingots. Die Ingots werden in 0,5 bis 1,5 mm dünne Scheiben, die sog. Wafer, zersägt. Die heute (2016) in der Massenproduktion verwendeten Siliciumwafer haben Durchmesser von 150, 200 oder 300 mm (auch 6, 8 oder 12 Zoll bezeichnet), während sich Wafer von 450 mm noch in der Einführungsphase befinden. Sie erhalten durch verschiedene Ätz-, Schleif- und Polierprozesse eine nahezu perfekte ebene Oberfläche mit Unebenheiten in der Größenordnung kleiner einem Nanometer, das heißt nur wenigen Atomlagen.

Front-End

Bei der Fertigung von integrierten Schaltkreisen werden alle Arbeitsschritte vor dem Zerteilen des Wafers unter dem Begriff Front-End (dt. etwa vorderer/erster Abschnitt) zusammengefasst. Sie erfolgt in Reinräumen, mit einer sehr geringen Dichte von Staubpartikeln. Dies ist nötig, weil selbst kleinste Partikel (< 0,1 µm) bereits den Ausfall eines kompletten Schaltkreises verursachen können. Die eingesetzten Prozesse und Verfahren lassen sich grob in folgende Gruppen unterteilen:

- Strukturierungsverfahren (vor allem die Fotolithografie zur Strukturierung von Fotolackmasken, die in den nachfolgenden Schritten Bereiche auf dem Wafer abdecken, die nicht behandelt (z.B. dotiert) werden sollen),

- Verfahren zum Schichtaufbau (Epitaxie, Sputterdeposition, Bedampfen, CVD usw.),

- Verfahren Schichtabtrag und Reinigung (trocken- und nasschemische Ätzprozesse) und

- Verfahren zur Änderung von Materialeigenschaften (z.B. Ausheizprozesse, Dotierung, Silizidbildung).

Die Front-End-Fertigung unterteilt sich nochmals in zwei größere Bereiche: das Front-End-of-Line (FEoL) und das Back-End-of-Line (BEoL). Sie unterscheiden sich sowohl hinsichtlich der zu fertigenden funktionellen Elemente als auch der eingesetzten Fertigungsverfahren der Halbleitertechnik und Materialien.

Ausgehend von einem unstrukturierten Wafer umfasst das Front-End-of-Line im Wesentlichen alle Prozessschritte für die Herstellung der elektrisch aktiven und passiven Bauelemente (Transistoren, Kondensatoren und auch Widerstände). Im Back-End-of-Line werden hingegen die elektrischen Verbindungen zwischen diesen Bauelementen gefertigt und so erst zu einer funktionierenden elektronischen Schaltung verknüpft. Im übertragenen Sinn werden hierbei Drähte, also dünne elektrische Leitungen aus Metall, gefertigt und gemäß dem Schaltplan verknüpft. Daher spricht man auch von Verdrahtung oder Metallisierung.

Grobe Trennlinie für das FEoL und das BEoL ist die Kontaktierung der Transistorelektroden. Die hierbei grundlegend verwendeten Verfahren entsprechen in großen Teilen dem im BEoL. Da in diesem kritischen Bereich jedoch spezielle Techniken und wiederum andere Materialien genutzt werden, ist dieser nicht klar einem der Bereiche zuzuordnen. Daher hat sich für diesen Fertigungsabschnitt die Bezeichnung Middle-of-Line etabliert.

Im Folgenden werden vereinfacht die wesentlichen Prozessfolgen für die Fertigung moderner, sogenannter Metall-Oxid-Halbleiter-Feldeffekttransistoren (MOSFET) innerhalb größerer integrierter Schaltkreise beschrieben.

Front-End-of-Line

Die Front-End-Fertigung eines typischen Mikroprozessors startet mit der Herstellung der Isolationsbereiche zwischen den einzelnen Bauelementen. Seit Ende der 1990er-Jahre wird hierzu weitgehend die sogenannte Grabenisolation (engl. shallow trench isolation, STI) genutzt. Hierbei werden zunächst große Grabenbereiche in das Substrat (meist Silizium) geätzt. Die Definition dieser Bereiche erfolgt über eine zuvor fotolithografisch strukturierten Lackmaske, die die späteren aktiven Transistorbereiche vor dem Ätzangriff schützt. Nach dem Ätzen werden die Gräben mit einem elektrisch isolierenden Material (meist Siliziumdioxid) aufgefüllt, meist mit Verfahren der chemischen Gasphasenabscheidung (CVD). Um sicherzustellen, dass keine ungefüllten Bereiche entstehen, wird deutlich mehr Nichtleitermaterial abgeschieden, als notwendig ist. Um anschließend wieder eine glatte Oberfläche zu erhalten, wird das überschüssige Material durch chemisch-mechanisches Polieren (CMP) abgetragen und die Waferoberfläche eingeebnet.

Nun folgt der nächste Fertigungsabschnitt, die Herstellung der sogenannten „Wannen“ (im Englischen wells) und der Vorbereitung des späteren Transistorkanals durch Dotierung des Substratmaterials. Dabei wird die extrinsische elektrische Leitfähigkeit des Substratmaterials lokal geändert. So entsteht beispielsweise durch Dotierung eines üblicherweise genutzten p-leitenden Silizium-Wafers (siehe auch Czochralski-Verfahren) mit Bor eine n-leitende Wanne, in dem anschließend die p-Kanal-Feldeffekttransistoren (FET), also ein Transistor, dessen Funktion auf der Ausprägung eines elektrisch p-leitenden Kanals basiert, hergestellt werden. Die Wannendotierung ist notwendig, um überhaupt die zwei unterschiedlichen Varianten von Feldeffekttransistoren (n-Kanal- und p-Kanal-Transistoren) für die seit einigen Jahrzehnten bei integrierten Schaltkreisen üblicherweise genutzte CMOS-Technik herstellen zu können. Darüber hinaus tragen die bei der Wannenherstellung entstehenden p-n-Übergänge dazu bei, die unterschiedlich dotierten Bereiche elektrisch zu entkoppeln. Die einfachste Variante ist der bereits beschriebene Einfachwannenprozess (hier für eine p-Wanne). Für bestimmte Anforderungen wird aber auch ein Zweifach- (p- und n-Wanne; engl. twin-well process) oder Dreifachwannenprozess (engl. triple-well process) verwendet. Die Dotierung selbst erfolgt heutzutage in der Regel mittels Ionenimplantation ganzflächig über den Wafer. Um die Bereiche zu schützen, die nicht oder anders dotiert werden sollen, werden diese mithilfe einer zuvor fotolithografisch strukturierten Lackmaske abgedeckt, diese wird wie üblich nach den Prozessen einer „Strukturierungs-Ebene“ durch nasschemische Prozesse (z.B. Piranha-Lösung) und/oder Plasmaveraschung entfernt. Diese gleichen Prozesse werden auch für die Dotierung des Transistorkanals eingesetzt. Im Unterschied zu den Wannen werden die Dotierungen jedoch nahe an der Oberfläche eingebracht. Zum Abschluss folgt in der Regel ein Temperaturprozess, der die bei der Ionenimplantation entstandenen Gitterstörungen ausheilt und die Dotierungen durch den Einbau in das Kristallgitter des Substrats elektrisch aktiviert.

Der dritte Prozessabschnitt dient dem Aufbau des Gate-Schichtstapels und der Gate-Strukturierung. Im Falle des in den 1990er- und 2000er-Jahren üblichen CMOS-Prozesses mit Siliziumdioxid als Gatedielektrikum und Polysilizium als Gateelektrode wird zunächst das sehr dünne (wenige Nanometer dicke) Gateoxid erzeugt, häufig durch „Rapid Thermal Oxidation“ (RTO, dt. etwa schnelle thermische Oxidation). Es folgt die ganzflächige Abscheidung eines Schichtstapels aus Polysilizium und einer dünnen Verkapselungsschicht aus Siliziumdioxid. Diese Oxidschicht wird mittels Fotolithografie und Ätzen strukturiert. Die entstehende strukturierte Schicht dient nach dem Entfernen der Fotolackmaske als Hardmaske für die Gatestrukturierung durch einen anisotropen Trockenätzprozess, reaktives Ionenätzen (RIE). Die Gatestrukturierung ist neben der Grabenisolation einer der anspruchsvollsten Prozesse im FEoL. Vor allem die Fotolithografie für die Definition der Gateelektrode stellt bis heute eine technische Grenze für die Miniaturisierung der (Planar-)Transistoren dar. Hier kommen hochspezialisierte Verfahren wie die Immersionslithografie, Verkleinerung der Linien der Fotolackmaske durch einen isotropen Trockenätzprozess (engl. resist shrink) und zunehmend auch Mehrfachstrukturierungen zum Einsatz. Auch der bereits erwähnte Zwischenschritt ist ein (relativ einfacher) Spezialprozess, der dadurch notwendig wird, dass die Fotolithografie unter anderem keine ausreichend dicken Fotolackmasken der notwendigen Auflösung bereitzustellen vermag, die den Ätzprozess überstehen würden.

Nach der Gatestrukturierung folgt, vereinfacht gesagt, die Definition der Source- und Drain-Gebiete. Im Fall älterer Technologieknoten (größer 350 nm) umfasste dies lediglich die spezielle Dotierung der Source- und Drain-Gebiete. Für die heutzutage typischerweise eingesetzten LDD-MOSFETs (LDD = engl. lightly doped drain) beinhaltet dies jedoch die Dotierung der Drain-Erweiterungs- (extension implant) und Halo-Implantate sowie die Herstellung von einem oder mehreren Spacern (dt. etwa „Abstandshalter“), über die sich die Position der durch Ionenimplantation eingebrachten Dotierungen verhältnismäßig leicht kontrollieren lässt. Erst am Ende folgt die abschließende Dotierung der Source- und Drain-Gebiete, mit denen der eigentliche FEOL-Fertigungsabschnitt endet. Nun beginnt die Kontaktierung und Verknüpfung der Transistoren.

Middle-of-Line

Nach der eigentlichen Transistorfertigung erfolgt die Verbindung der einzelnen Bauelemente. Bevor dies geschieht, müssen jedoch zunächst die Transistorelektroden elektrisch kontaktiert werden. Der Abschnitt der Kontaktfertigung wird nicht eindeutig dem FEOL oder BEOL zugeordnet, deshalb wird dieser Abschnitt auch häufig als Middle-of-Line (MOL) bezeichnet.

Um einen guten elektrischen Kontakt der halbleitenden Bereiche und der metallischen Verbindung zu gewährleisten (vgl. Schottky-Kontakt), werden die Elektroden zunächst silizidiert, beispielsweise durch ganzflächige Abscheidung einer Nickelschicht und nachfolgender Silizid-Bildung bei hohen Temperaturen. Nach der Silizidbildung folgt in der Regel die Abscheidung und Einebnung des Zwischendielektrikums – meist undotiertes Silikatglas (engl. undoped silcat glass, USG) oder Low-k-Dielektrika (zunehmend seit Mitte der 2000er Jahre). Anschließend folgt die Herstellung der Kontaktlöcher mittels RIE und deren Füllung mit einem Metall, meist Wolfram, das über CVD-Verfahren abgeschieden und mittels CMP eingeebnet wird.

Auch die bei einigen Transistortechnologien genutzten Verspannungsschichten, die Druck oder Zug auf den Transistorkanal ausüben sollen und somit die Ladungsträgerbeweglichkeit beeinflussen können, werden meist nach der Silizidbildung aufgebracht und dem MoL zugeordnet.

Back-End-of-Line

Nun folgt das eigentliche BEOL der Metallisierung, das heißt die Herstellung eines Netzwerks aus Leiterbahnen, mit denen die einzelnen Bauelemente verbunden werden. Typische Materialien sind Aluminium bzw. seit Ende der 1990er oft auch Kupfer. Die Herstellung der Leiterbahnen ist dabei stark vom verwendeten Metall abhängig. So wird bei Aluminium in der Regel zunächst das Metall ganzflächig abgeschieden und anschließend mithilfe der Fotolithografie und einem Trockenätzprozess strukturiert. Diese Methode ist bei Kupfer nicht möglich, da es keinen Trockenätzprozess für Kupfer gibt, bei dem gasförmige Reaktionsprodukte entstehen. Es gibt seit den frühen 2000er Jahren jedoch erfolgreiche Forschungsarbeiten, Kupfer im Hochvakuum mit Trockenätzverfahren zu strukturieren. Stattdessen erfolgt bei Kupfer zunächst eine Strukturierung der ganzflächig abgeschiedenen Isolationsschicht und danach die Kupfermetallisierung mittels galvanischer Verfahren. Hierbei kommen im Wesentlichen zwei Techniken zum Einsatz: der Damascene- und Dual-Damascene-Prozess. Sie unterscheiden sich in der Art, wie die elektrischen Verbindungen, genannt VIA (englisch vertical interconnect access), zwischen den eigentlichen Leiterbahnebenen gefertigt werden (einzeln oder zusammen mit den Leiterbahnebenen). Die VIAs entsprechen den Durchkontaktierungen bei mehrschichtigen Leiterplatten. In der Abbildung sind es die orange, senkrechten Strukturen. In einem fertigen integrierten Schaltkreis befinden sich dann 13 bis zu 15 solcher Metallisierungsebenen übereinander. Die Strukturgröße nimmt dabei stufenweise in höheren Ebenen zu, beispielsweise sind die ersten beiden Ebenen in der kleinstmöglichen Strukturgröße (1×) gefertigt und anschließend folgen zwei bis fünf Ebenen mit einem größeren Strukturabstand (z.B. 2×) dies sich bis zu 32-fach (32×) gröberen Strukturen in der obersten Ebene fortsetzen (Zwischenstufen können dabei ausgelassen werden).

Neben dieser konventionellen Metallisierung gibt es auch weitere Techniken wie Silizium-Durchkontaktierung (englisch through-silicon via, TSV). Sie wird derzeit bei einigen Sensoranwendungen eingesetzt, bei denen bestimmte Funktionen sowohl auf der Vorder- als auch auf der Rückseite der Chips benötigt werden, beispielsweise bestimmte Biosensoren. Sie gilt aber auch als eine zukunftsträchtige Technik zur Realisierung einer künftigen 3D-Integration von integrierten Schaltkreisen. Dabei werden mehrere (stark abgedünnte) Chips übereinander gestapelt und die einzelnen Chipebenen elektrisch durch TSVs miteinander verbunden. Da in beiden Fällen die TSVs durch den Wafer verlaufen, spricht man auch von wafer level through-silicon via (dt. Silizium-Durchkontaktierung durch den Wafer).

Bei einigen Bauelementen, wie beispielsweise IGBT, wird zusätzlich die der Schaltung entgegengesetzte Seite metallisiert, um einen leitenden Kontakt herzustellen; allerdings mit nur einer oder zwei Metallisierungsebenen.

Back-End

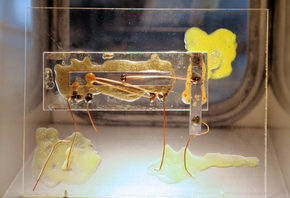

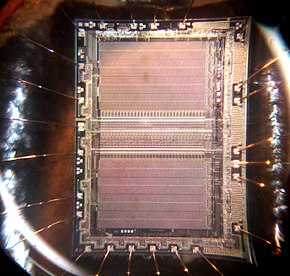

Zur Verwendung auf einer Leiterplatte muss der empfindliche Chip in ein Gehäuse eingebaut werden.

Im sogenannten Back-End werden die Wafer in die Einzelchips zerteilt und diese in der Regel in ein Gehäuse eingebracht.

Vor dem Zerteilen werden die Wafer häufig durch Schleifen abgedünnt, das sogenannte „Backlapping“. Die Wafer sind danach nur noch ca. 100 bis 200 µm dick. Die Abdünnung wird vorgenommen, um das Kühlverhalten des Chips zu verbessern. Dies ist möglich, da sich bei integrierten Schaltkreisen in Dünnschichttechnik elektrisch aktive Gebiete nur in den ersten Mikrometern an der Oberfläche der Strukturseite befinden. Das restliche Substratmaterial dient nur noch der mechanischen Stabilität. Bei gesägten Chips ist die volle Substratdicke nicht mehr notwendig. Dicke Substrate weisen jedoch einen höheren Wärmeleitwiderstand auf. Da die Kühlkörper in der Regel auf der Substratrückseite angebracht werden, besitzen abgedünnte Wafer ein besseres Kühlverhalten.

Das Zerteilen der Wafer in die einzelnen Dies erfolgt in der Regel durch Sägen, selten auch durch Ritzen und Brechen. Damit die Dies beim Sägen nicht auseinanderfallen, wird vor dem Sägen der Wafer auf eine Sägefolie aufgeklebt. Da die Säge ein Stück aus dem Wafer entfernt, sind die Chips nicht nahtlos nebeneinander angeordnet, sondern haben einen gewissen Abstand. In diesen Bahnen, dem sog. „Ritzrahmen“, sind zudem Teststrukturen aufgebracht, die unter anderem zur PCM-Messung unmittelbar nach der Front-End-Fertigung genutzt werden. Diese Teststrukturen werden beim Sägen zerstört.

Beim nachfolgenden Verpacken (engl. packaging) werden die einzelnen ICs dann in ein Gehäuse eingebracht und kontaktiert, das sogenannte Bonden. Dabei kommen je nach Typ unterschiedliche Verfahren zum Einsatz, beispielsweise Chipbonden oder Drahtbonden. Das Verkappen (Einhausen) dient zur hermetischen Versiegelung gegenüber Umwelteinflüssen – für rein elektrische Schaltkreise muss das Gehäuse gas- und lichtdicht sein – sowie zur besseren Verwendbarkeit. Entweder wird der Chip samt Bonddrähten in einem Hohlraum (Blech, Keramik, ggf. mit Fenster) eingeschlossen oder mit Kunstharz umhüllt (eingegossen, Spritzgusstechnik). Hochkomplexe Schaltkreise (meist für mobile Anwendungen) werden neuerdings (2009) auch ohne Sockelgehäuse eingesetzt und direkt auf die jeweiligen Platinen gelötet. Zum Abschluss erfolgt nochmals ein Funktionstest, dabei werden zugesicherte Eigenschaften an allen Schaltkreisen geprüft. Die Typprüfung erfolgt stichprobenartig oder nur in der Entwicklungsphase. Die Stückprüfung dient dem Sortieren in Schaltkreise unterschiedlicher Güteklassen (zum Beispiel nach Offset-Spannung bei Operationsverstärkern) Prüfergebnisse und die Art der Verkappung bestimmen das Einsatzgebiet. So werden hohe Qualitäten für erweiterte Einsatztemperaturen und Umweltanforderungen gefertigt (sog. MIL-Standard für militärische und Raumfahrt-Anwendungen). Höhere Toleranzen und Plastik-Verkappung kommen für Massenanwendungen (Konsumgüter) in Frage.

Als letzter Schritt wird das Gehäuse mit Informationen des Herstellers bedruckt, z.B. mit dem Herstellernamen, der Typennummer, dem Herstellungsdatum u.ä. Die Back-End-Fertigung wird im Gegensatz zur Front-End-Fertigung von Mikromechanik und Verfahren der Kunststoffbearbeitung (Spritzguss) dominiert.

Funktionstests und Prozessüberwachung

Um schon frühzeitig auf Prozessschwankungen zu reagieren, fehlerhafte Prozesse gegebenenfalls zu korrigieren oder gar Wafer oder Lose aus der Produktion zu nehmen, werden die noch unfertigen ICs nach vielen Prozessschritten getestet. Im Front-End handelt es sich dabei meist um Stichproben in Form eines PCM-Tests (engl. process control monitoring, dt.: Prozessüberwachung). Für die Bestimmung von technologischen Parametern erfolgt die Prüfung (beispielsweise Schichtdickenprüfung) meist direkt nach dem jeweiligen Prozess, hier ist es mitunter wichtig auch die jeweiligen Anlagen mit zu erfassen, da auch baugleiche Anlagen mit denselben Parametern Abweichungen erzeugen, die außerhalb des Toleranzbereichs liegen können. Nach dem Front-End werden in der Regel alle ICs vor der Weiterverarbeitung auf ihre Funktion getestet. Dabei werden die wichtigsten elektrischen Parameter der verwendeten Bauelemente an speziellen Teststrukturen ermittelt, die sich in den Ritzgräben zwischen den Chips befinden. Die Parameter müssen bestimmte Spezifikationen einhalten, um sicherzustellen, dass die Chips im gesamten zulässigen Temperaturbereich und über die volle spezifizierte Lebensdauer zuverlässig arbeiten. Teilweise sind bestimmte Funktionen (HF-Schaltungen oder später nicht auf PINs herausgeführte Anschlüsse des Chips) nur auf dem Die testbar. Vor allem muss aus Kostengründen verhindert werden, dass nicht funktionsfähige ICs im nachfolgenden Herstellungsprozess weiterbearbeitet werden.

Obwohl diese Messungen auf speziellen Testsystemen (Automatic Test Equipment) vollautomatisch ablaufen, haben die damit verbundenen Kosten bei hochintegrierten Prozessorchips bereits nahezu die Herstellungskosten erreicht. Dies liegt vor allem daran, dass nur bedingt Skaleneffekte beim Testen greifen (eine Parallelisierung ist beispielsweise nur bei reinen Digitalschaltungen möglich) und neuere ICs immer mehr Funktionen beinhalten, die nacheinander getestet werden müssen. Um die feinen Strukturen der Mikroelektronik auflösen zu können, werden heutzutage Starrnadeladapter eingesetzt, mit welchen ein Messpunktabstand von 150 µm aufgelöst werden kann. Durch das präzise Führen der Starrnadeln können mit solchen Adaptern Kontaktstellen mit einem Durchmesser von 70 µm abgegriffen und geprüft werden. Als weiteres ermöglicht der Starrnadeladapter auch das Kontaktieren von feinpoligen Mikrosteckern, welche heutzutage in der Mikroelektronik immer mehr ihre Anwendung finden. Somit müssen solche Stecker nicht mehr mit dem schnell verschlissenen Gegenstecker kontaktiert werden. Bei allen neuen FE-Technologien wird eine Lernkurve durchlaufen, die sich u.a. an der Ausbeute funktionierender Bausteine messen lässt (Yield). Da eine neue FE Technologie erhebliche Entwicklungskosten (z.T. 3-stellige Millionenbeträge) beinhaltet, haben die Firmen ökonomische Vorteile, die möglichst schnell hohe Yield Werte erzielen.

Schließlich wird auch der gehäuste Chip vor der Ablieferung einem endgültigen Test unterzogen, um Fehler in der Back-End-Fertigung festzustellen. Auch werden einige Eigenschaften getestet, die sich durch das Packaging verändern, bzw. deren Messung ohne Gehäuse nicht möglich ist, wie z.B. das Bonding oder bestimmte Hochfrequenzeigenschaften. Der gehäuste Chip kann dann zur Leiterplattenbestückung gehen.

Miniaturisierung

Integrierte Schaltkreise werden als eigenständiges elektronisches Bauteil betrachtet. Die Größe des IC-Substrats (englisch die) beträgt dabei in der Regel nur wenige Quadratmillimeter und ist erheblich kleiner als das umgebende Gehäuse, das die eigentlichen elektrischen Anschlüsse (Pins) in handhabbarer Größe zum Verlöten bereithält. Um die Produktionskosten der oft komplexen und herstellungsaufwendigen ICs möglichst gering zu halten, werden in der Mikroelektronik mehrere (hundert bis tausend) integrierte Schaltkreise parallel auf so genannten Wafern hergestellt, die dabei auftretenden Produktionstoleranzen und -fehler verhindern allerdings eine hundertprozentige Ausbeute.

Um die Produktionskosten in nachfolgenden Generationen komplexerer ICs möglichst konstant zu halten oder gar zu senken, werden in der Mikroelektronik zwei große Trends vollzogen. Zum einen wird die Chip-Fläche für den einzelnen IC möglichst gering gehalten (Haupttrend) zum anderen werden möglichst viele ICs auf einem Wafer untergebracht, während das Gehäuse anderen Anforderungen Rechnung trägt (Löttechnologie, Wärmeableitung etc.) und je nach Marktanforderung auch verschiedene Ausprägungen zeigt.

Die möglichst konstant gehaltene Chip-Fläche hat bei immer komplexer werdenden Schaltkreisen zur Folge – moderne integrierte Schaltkreise wie z.B. Speicherbausteine und Mikroprozessoren können einige Milliarden Bauteile (insbesondere Transistoren) enthalten –, dass die einzelnen Bauelemente wie Transistoren verkleinert werden müssen, was ebenfalls eine höhere Taktung und eine verringerte Betriebsspannung und daher Leistungsaufnahme ermöglicht. Bei konstanter Chip-Fläche können aber kaum Kosten durch höhere Parallelität bei der Herstellung gespart werden. Daher wurde die Standard-Wafer-Größe in der Produktion von 2-Zoll-Wafern auf heute 12-Zoll-Wafern (wirklicher Durchmesser 300 mm) erhöht. Mit der steigenden Wafer-Größe ging auch eine effizientere Ausnutzung der Wafer-Fläche einher (weniger Verschnitt). Um allerdings die Produktionsqualität dabei nicht nur gleich zuhalten, sondern zu verbessern – was aufgrund kleiner Bauelemente notwendig war – mussten große Herausforderungen in der Beschichtungstechnologie überwunden werden.

Im Allgemeinen werden also bei der Miniaturisierung der Schaltkreise folgende Ziele verwirklicht:

- Ein Ziel ist eine effizientere Fertigung, dies wird unter anderem durch parallele Fertigung auf einem Substrat (englisch wafer) und somit der Einsparung von Rohstoffen bei der Produktion und der Weiterverarbeitung erreicht.

- Weiterhin sollen die Bauelemente effizienter im Betrieb werden, so ermöglicht die Verkleinerung der Strukturen eine Erhöhung der Schaltgeschwindigkeiten, dies wird beispielsweise durch kürzere Leitungslängen und somit kürzere Signallaufzeiten sowie geringeren Latenzzeiten beim Umladen der Kapazitäten in den Bauelementen erreicht, und durch Verringerung der Leistungsaufnahme der ICs.

- Durch die Integration weiterer Funktionen können neue ICs oft die Funktionalität mehrerer vorher diskreter ICs in sich vereinen, damit kann auch die Zuverlässigkeit erhöht werden, was vor allem in der Anfangsphase der integrierten Schaltkreise ein wichtiger Vorteil gegenüber konventionellen, gelöteten Schaltungen darstellte.

Auf diese Weise sollen kleinere, leistungssparendere Bauelemente mit immer mehr Funktionen hergestellt werden, dies ist vor allem bei mobilen Geräten wichtig. Die integrierten Schaltungen und deren Miniaturisierung ermöglicht so Telefon-, SIM-, Geld- und Kreditkarten, RFID, intelligente Sensoren, kleinere und langlebigere Herzschrittmacher oder Hörgeräte sowie MP3-Abspielgeräte oder CMOS-Kameras, u.a. in Mobiltelefonen.

Anwendungsbereiche

Integrierte Schaltkreise bilden heute die Grundlage jeglicher komplexer Elektronik, insbesondere der Computertechnik. Erst durch die Integration ist es möglich, umfangreiche Funktionalität auf kleinem Raum zur Verfügung zu stellen. Darüber hinaus ermöglichen integrierte Schaltkreise in vielen Fällen überhaupt auch erst die technische Realisierung von Systemen, die sonst zu teuer, zu komplex, zu leistungsintensiv, zu groß bzw. prinzipiell nicht machbar wären.

© biancahoegel.de

Datum der letzten Änderung: Jena, den: 21.11. 2024